我們在買內存的時候最關注的或許就是容量,再然後就是頻率,但是還有人會選擇看時序,高頻低時序的內存都比較貴,那麼時序到底是什麼東西呢?

我們這次要介紹的是內存的時序,這應該是內存除容量、標準、頻率外最重要的參數,然而說清楚它是什麼,還是需要一定的參考資料才能理清,而且其中還有些容易混淆 的概念、單位,甚至需要進行簡單的換算。 大家上中學的時候應該都有聽老師說過最容易忽視的知識點最需要復習,所以我們今天來看看,作為或許是最重要部件之一的內存,所謂的時序到底是什麼意思。

.jpg)

這款內存的時序則是CL16-18-18-38

時序是什麼樣子的?

我們說簡單點,所謂的內存時序,英文是”Memory Timing“,一般來說都標註在內存條散熱片,通常以數字的形式寫作”TT-XX-YY-ZZ“,當然有些是只標註前 三節的,不過也有標註五節的,但反映的都是都是內存在不同工作環節當中的延遲時間,但需要注意的這裡的時序只是性能指標,單位是時鐘週期(Clock Cycles),數值越低 意味著性能越強大,而真正決定平台性能水平的延遲時間單位是納秒(ns,nanosecond)。

這是一條比較早的DDR2內存,時序是CL:4-4-4-12,不過電壓按照現在的標準就真的很高

時序完整的意義包括什麼?

完整的時序參數包括四節數字,分別是CL(CAS Latency)、tRCD(Row Address to Column Address Delay)、tRP(Row Precharge Time)、tRAS(Row Active Time)。 看上去是不是有點迷糊? 其中翻譯成中文其實就是列地址訪問潛伏時間(CL)、行地址到列地址等待時間(tRCD)、行地址預充電時間(tRP)、行地址活動時間(tRAS)。 其實時序就是內存在工作中需要的,或是必要的周期數(Cycles),所以周期越少才意味著越強的性能,而不是我們經常在CPU、GPU當中積累的邏輯:越高的數字代表 著越快的處理速度。 所不同的是,CL值,也就是時序當中首個數字是確切的周期數,而後面的三個數字都是最小周期數。

從原理來看,各種延遲週期都是什麼

但這些參數到底代表著什麼呢? 我們都應該知道,就傳統的SDRAM內存而言,每顆內存顆粒當中的存儲單元其實是採用類似於棋盤的二維架構,這種架構我們稱之為“Bank”,其中縱向我們稱之為行 (Row),或者說Word Line(Word=2 Byte),而橫向我們稱之為列(Columns),或者說Bit Lines。 而當歷史發展到DDR,“Bank”隨之發展到“Rank”,當處理器需要處理內存當中緩存的信息,首先需要尋址,這里首先要先確定行(Row),再確定列(Columns) ,或者說要讓行數據和列數據有效激活,所以這時候首先就需要接觸到的是時序參數中的“tRCD”,或者說“RAS to CAS Delay”,顧名思義就是發送列有效數據和行有效數據 之間的間隔,所以如果tRCD=9,就說明需要9個週期(Clock),結合頻率接可以推算到具體多少納秒(ns)。

圖片來自 AnandTech

在確認行數據和列數據後,其實就已經確定具體的存儲單元,這時候我們需要接觸時序中的第一個參數:“CAS Latency”,這裡的“Latency”一般理解為”潛伏“而不是“ 延遲”。 這裡衡量的是在將列數據(Column Address Strobe)數據和讀取命令發送後,到輸出最初的數據之間的潛伏期,單位同樣是周期(Clock)。

CAS Latency時序週期,圖片來源於 HardSecret

在進行一次行-列操作後,我們接下來需要的是對另一行繼續這種操作,而這時候需要將之前的工作關閉,然後重新確認行地址、列地址,這中間是需要關閉工作,然後 進行預充電的(Precharge),這裡我們就需要接觸時序參數當中的第三項:“tRP”。 預充電具體的意義和操作比較複雜,準確來說是發出預充電命令後,需要等待才能允許行數據(Row Address Strobe)工作的等待時間,也可以簡單理解為完成一次行-列工作,需要準備 進行下一次循環工作的準備時間,單位同樣是周期(Clock)。

此外還有“tRAS“,它衡量的其實接近一個時間窗口,或者說周期窗口,準確來說是當激活行命令發起時,到進行下一次預充電時間命令之間的周期窗口,也就是對進行 下一次預充電的時間進行限制。

既然這樣,週期更低的時序一定更強嗎?

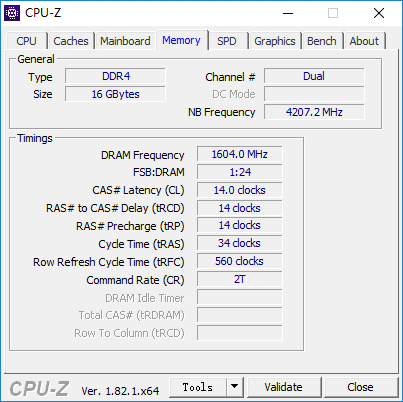

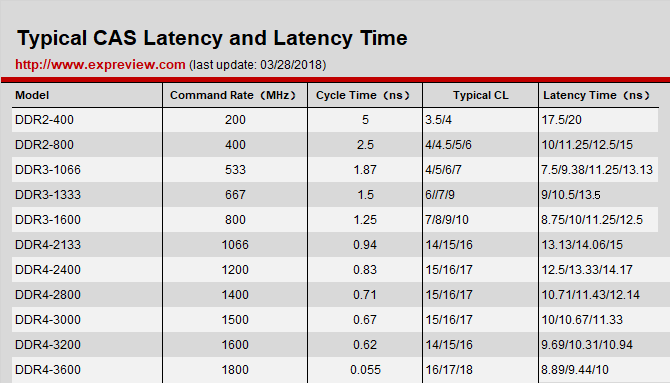

然而時序並不是這麼簡單單純的內容,比如說你不能忽視內存的標準和頻率,僅僅看到時序所代表的周期數就判定背後的性能孰優孰劣。 以我們常見的 DDR3 、DDR4內存來說,我們來看看時序和背後的真正的延遲時間。 首先我們知道DDR內存存在Dual Data Rate的特性,所以在時鐘週期的上升沿和下降沿各傳輸一次信號,所以我們插入一塊DDR3-1600MHz的內存,在CPU-Z當中看到的頻率就是800MHz,我們 就以800MHz為例,換算過來的周期時間就是1.25ns/週期,那麼以我們常見的DDR3 CL=10為例,實際的延遲時間就是10.25ns,但是我們找一條頻率更高的DDR3-2133MHz內存, 那麼背後實際的頻率就是1066MHz,那麼換算過來的周期時間就是0.938ns/週期,這樣就算不用算,我們也知道相同的時序,頻率更高的內存會有更短的實際延遲時間,所以說,雖然 更低的時序會確實代表著所需要的周期更少,但是更快的頻率同樣很重要。

不過更加有經驗的讀者應該知道,即使這些說的都對,也只能說在給定的時序,或者說CAS延遲週期環境中,越高的頻率意味著越短的延遲時間,而現實情況是 ,如果你瀏覽一遍我們內存的發展,不用考慮電壓、預存取位數,只看頻率和CL週期的話,會發現越高的頻率,往往會有越高的CL週期,我們以前使用很主流的 DDR3-1600MHz內存的時候,常見的CL週期大致是在8-10左右,而如果是現在很常見的XMP頻率:3200MHz的話,CL週期會達到14-16左右,如果再達到3600MHz的話,CL=17 、CL=18都能看的到。 所以既不可以光看時序,也不能只看頻率,高頻率、低時序週期才能帶來最優的延遲時間。

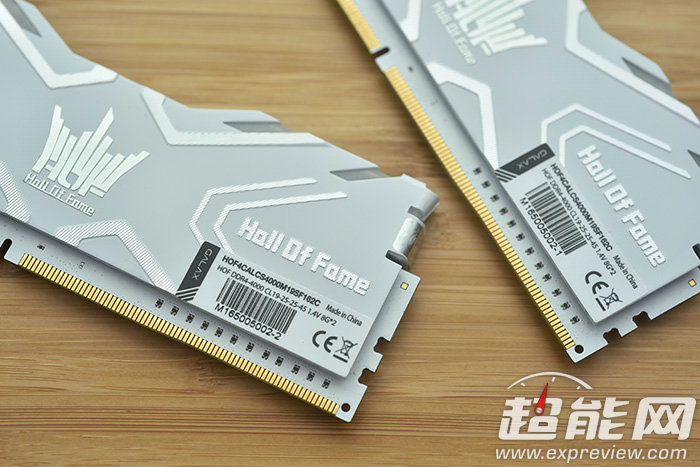

這款影馳名人堂DDR4-4000MHz內存頻率很高,但時序(CL19-25-25-45)同樣很高

雖然我們在大部分看到時序的時候,標註的都是CL=X,看上去CL似乎是曝光度最高的時序項目之一,但其實其他項目也需要知道,在完整的CL-tRCD-tRP- tRAS-T時序項目當中,除我們已經介紹過的CL,還有其他需要注意的地方,比如說從數字角度來說,前三項雖然沒有必然的大小關係(但絕大多數時候是CL>tRCD >tRP>tRAS)大家經常會注意到第四項tRAS經常是數字最大的項目,在以前DDR的時候,tRCD的數值會比較大,大致等於tRCD+2xtRAS,比如說CL4-4-4-12( 雖然現在一般很少有這麼極端,一般來說都是tRAD略大於2xtRP,比如說CL17-18-18-18-38)。 而如果完整標出第五項的話,大家會見到1T/2T,也有些做1N/2N,這部分叫做首命令延遲(Command Rate),衡量的是在選擇單個內存P-Bank芯片集後多少時間 可以發出具體的尋址的L-Bank命令,也就是上面的CL、tRCD之間,衡量的單位也是時鐘週期,因此也是越短越好,1T的性能會稍稍優於2T,但是反過來說對於 穩定性這是一種考驗。

所以這條內存的完整時序是14-14-14-34-2T

所以總的來說,其實內存還是比較少內容是可以給大家來推敲的,也就只有頻率、時序這些概念,而對於時序,其實大家只要知道這是內存在和處理器工作交換數據時需要發生 的周期就好(注意是周期而不是性能,單位是cycle/clock,而不是ns),越低的周期意味著越好的性能,結合高的內存頻率可以帶來最低的延遲時間,但總的 來說越高的內存頻率還會帶來越高的時序,總之大家結合低時序和高頻率就好。

頭條楓林網

頭條楓林網